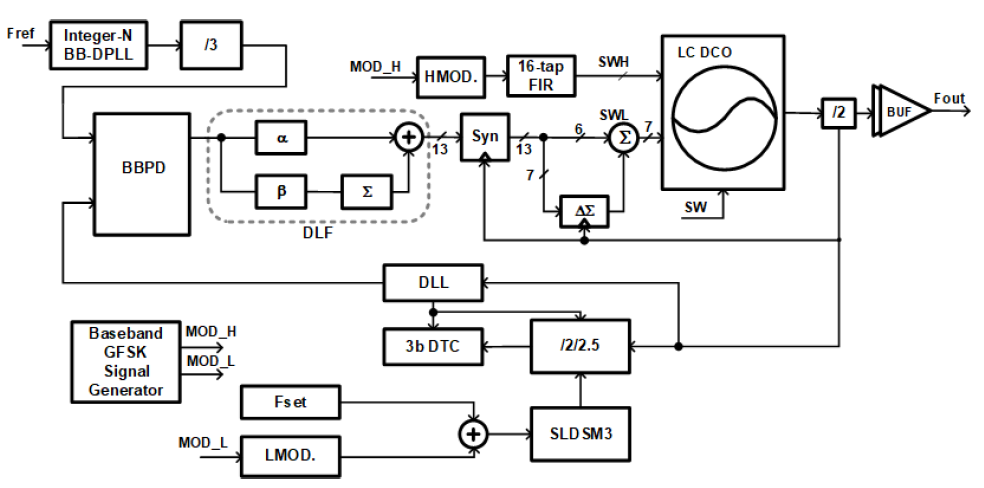

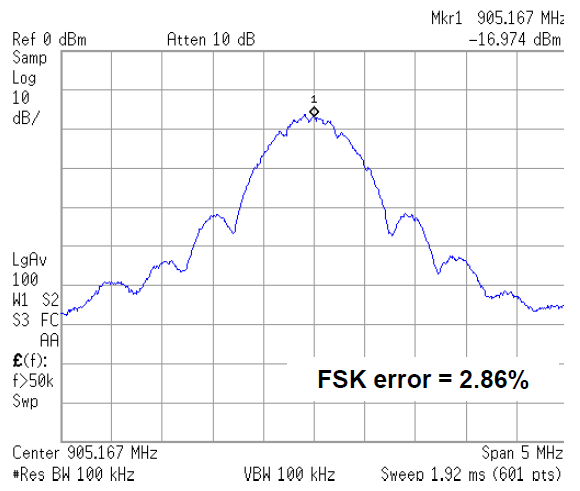

采用65nm CMOS工艺设计并实现了一款基于PCIe协议的5GHz时钟调制器,该时钟调制器使用两级结构和带内噪声整形技术以实现可观的带内噪声性能,同时采用了双环结构使得无需增益校准的两点调制器成为可能。

采用中芯国际14nm FinFET工艺进行流片,完成了超低电压锁相环时钟产生系统的设计。采用了环形振荡器作为锁相环的核心部分,通过差分环形滤波器对振荡器进行控制。芯片有源区面积约60×80µm2,最低功耗可以达到0.265mW。

已发表了JSSC/T-MTT/TCAS-II期刊和CICC/RFIC/A-SSCC的国际会议论文。